Centro Universitario UAEM Zumpango

# Ingeniería en Computación

Lógica Secuencial y Combinatoria

Dr. Arturo Redondo Galván

Centro Universitario UAEM Zumpango

# LÓGICA SECUENCIAL Y COMBINATORIA

**UNIDAD V**

Lógica Combinatoria

Centro Universitario UAEM Zumpango

### **OBJETIVOS:**

Analizar y diseñar de manera eficiente, sistemas lógicos modulares, tales que permitan el desarrollo de proyectos electrónicos aplicando la tecnología computacional, los dispositivos electrónicos y sistemas de tipo comercial y de vanguardia para resolver problemas propios de su ámbito profesional.

Centro Universitario UAEM Zumpango

## **INTRODUCCIÓN (1/2)**

- Los circuitos lógicos se dividen en combinacionales y secuenciales.

- Los circuitos combinacionales son aquellos cuya salida depende únicamente de la combinación presente en las entradas.

- Un circuito combinacional consiste en variables de entrada, compuertas lógicas y variables de salida.

- En los circuitos secuenciales las salidas dependen de las entradas y del estado que guarde el circuito, es decir, depende también de los elementos de almacenamiento.

Centro Universitario UAEM Zumpango

# INTRODUCCIÓN (2/2)

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (1/8)

- El análisis de un circuito combinacional implica determinar la función que realiza el circuito.

- El primer paso consiste en asegurarse que el circuito sea combinacional, es decir, que este **formado por compuertas lógicas** sin trayectorias de retroalimentación, ni elementos de memoria.

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (2/8)

- Rotule las salidas de las compuertas que están en función de las variables de entrada. Obtenga la función de salida de cada compuerta.

- Repita el paso anterior para las compuertas que dependan de los rótulos anteriores.

- 3. Realice las sustituciones de las funciones previamente definidas del tal manera que la función de salida dependa únicamente de las entradas.

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (3/8)

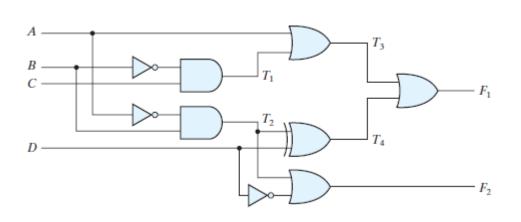

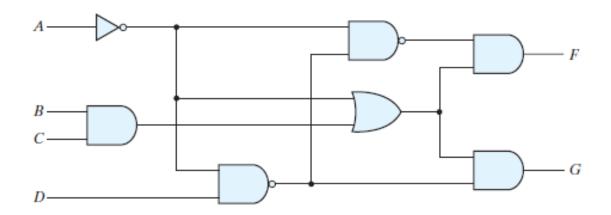

Ejemplo: obtener las funciones de salida del siguiente circuito.

$$T_{1} = B'C$$

$T_{2} = A'B$

$T_{3} = A + T_{1} = A + B'C$

$T_{4} = T_{2} \oplus D = T_{2}D' + T_{2}'D$

$T_{4} = (A'B)D' + (A'B)'D$

$T_{4} = A'BD' + (A+B')D$

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (4/8)

Ejemplo: obtener las funciones de salida del siguiente circuito.

$$F_1 = T_3 + T_4 = A + B'C + (A'BD' + (A + B')D) = A + B'C + A'BD' + AD + B'D$$

$F_1 = A + BD' + B'C + B'D$

$F_2 = T_2 + D' = A'B + D'$

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (5/8)

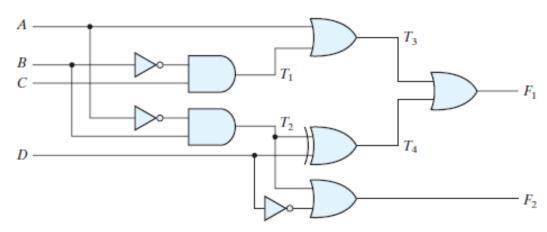

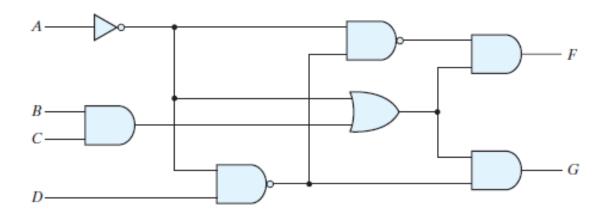

Ejercicio: obtener las funciones de salida del siguiente circuito.

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (6/8)

Para obtener la tabla de verdad es debe el siguiente procedimiento:

- 1. Realizar las 2<sup>n</sup> combinaciones de las *n* variables de entrada.

- 2. Rotular las salidas de las compuertas.

- 3. Obtener las salida de cada función rotulada.

- 4. Obtener la salida del circuito.

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (7/8)

Ejemplo: obtener la tabla de verdad del ejemplo anterior.

```

0000

0 0 0 1

0 0 1

0 0 1 0

0 0 1 1

0100 0 1 0

0 1 0 1

1 0

0 1 1 0 0 1 0

0 1 1 1

1 0 0 0

1001

1 0 1 0

1

1 0 1 1

0 1

1

0

1 1 0 0

1 1 0 1

0

1 1 1 0

1 1 1 1

0

```

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE ANÁLISIS (8/8)

Ejercicio: obtener la tabla de verdad del siguiente circuito.

Centro Universitario UAEM Zumpango

## PROCEDIMIENTO DE DISEÑO (1/10)

- El diseño de un circuito combinacional inicia con la **especificación del problema** y finaliza con el **diagrama lógico** del circuito.

- Para realizar el diagrama lógico es necesario obtener previamente las **funciones de salida** del circuito lógico.

Centro Universitario UAEM Zumpango

## PROCEDIMIENTO DE DISEÑO (2/10)

- 1. Deducir el numero de entradas y salidas.

- Obtener la tabla de verdad.

- 3. Deducir las funciones de salida simplificadas.

- 4. Dibujar el diagrama lógico.

Centro Universitario UAEM Zumpango

## PROCEDIMIENTO DE DISEÑO (3/10)

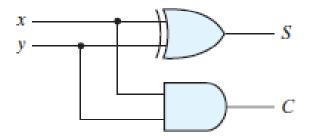

Ejemplo: diseñar un medio sumador. El circuito realiza la suma de dos bits de entrada.

- 1. El circuito necesita dos bits de entrada y dos bits de salida. Las variables de entrada son x, y y las variables de salida S (suma) y C (acarreo).

- 2. Obtenemos la tabla de verdad.

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE DISEÑO (4/10)

Ejemplo: diseñar un medio sumador. El circuito realiza la suma de dos bits de entrada.

De la tabla de verdad se obtienen directamente las funciones de salida o utilizando mapas de Karnaugh.

$$s = x'y + xy'$$

$$c = xy$$

Centro Universitario UAEM Zumpango

# PROCEDIMIENTO DE DISEÑO (5/10)

Ejemplo: diseñar un medio sumador. El circuito realiza la suma de dos bits de entrada.

4. De las funciones obtenemos el diagrama lógico.

Centro Universitario UAEM Zumpango

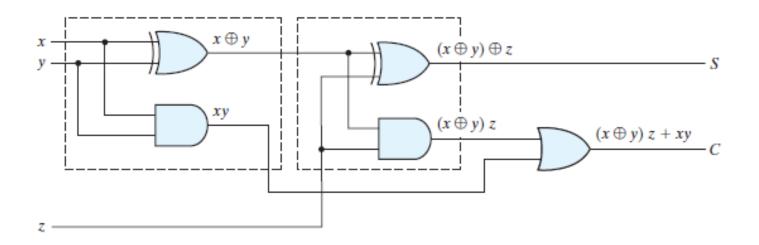

## PROCEDIMIENTO DE DISEÑO (6/10)

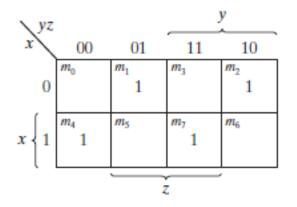

Ejemplo: diseñar un medio sumador completo. El circuito realiza la suma de tres bits de entrada.

- 1. El circuito necesita tres bits de entrada y dos bits de salida. Las variables de entrada son x, y y z y las variables de salida S (suma) y C (acarreo). z representa el acarreo de la posición más significativa inmediata anterior.

- 2. Obtenemos la tabla de verdad.

```

x

y

z

C

S

0

0

0

0

0

0

0

0

1

0

1

0

1

1

0

0

1

1

0

0

0

1

1

0

1

0

1

0

1

1

0

1

0

1

1

1

1

1

1

1

```

Centro Universitario UAEM Zumpango

## PROCEDIMIENTO DE DISEÑO (7/10)

Ejemplo: diseñar un medio sumador completo. El circuito realiza la suma de tres bits de entrada.

De la tabla de verdad se obtienen las funciones de salida utilizando mapas de Karnaugh.

$$S = x' y' z + x' yz' + xy' z' + xyz$$

$$S = (x' y + xy')z' + (x' y' + xy)z$$

$$S = (x' y + xy')z' + (x' y + xy')'z$$

$$S = x \oplus y \oplus z$$

Centro Universitario UAEM Zumpango

## PROCEDIMIENTO DE DISEÑO (8/10)

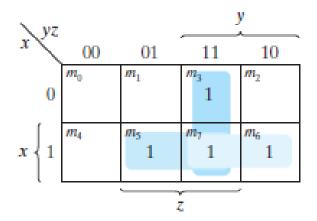

Ejemplo: diseñar un medio sumador completo. El circuito realiza la suma de tres bits de entrada.

De la tabla de verdad se obtienen las funciones de salida utilizando mapas de Karnaugh.

$$C = xy + xz + yz$$

$$C = (xy'+x'y)z + xy$$

$$C = (x \oplus y)z + xy$$

Centro Universitario UAEM Zumpango

## PROCEDIMIENTO DE DISEÑO (9/10)

Ejemplo: diseñar un medio sumador completo. El circuito realiza la suma de tres bits de entrada.

4. De las funciones obtenemos el diagrama lógico.

Centro Universitario UAEM Zumpango

### PROCEDIMIENTO DE DISEÑO (10/10)

Ejercicio 1: diseñar un medio restador. El circuito realiza la diferencia de dos bits de entrada.

Ejercicio 2: diseñar un restador completo. El circuito realiza la diferencia de dos bits de entrada, tomando en cuenta que un 1 se ha tomado de la etapa significativa más baja.

Centro Universitario UAEM Zumpango

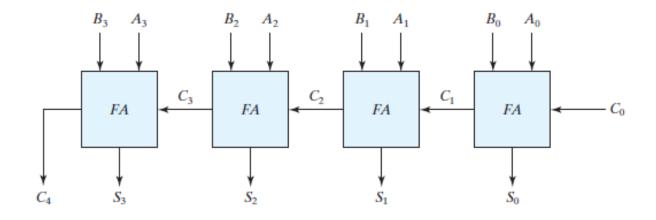

### **SUMADOR BINARIO (1/2)**

- El sumado binario es un circuito combinacional que realiza la suma de dos números binarios.

- El circuito es posible construirlo por medio de sumadores completos conectados en cascada.

- El acarreo de salida de cada sumador completo se conecta al acarreo de entrada del siguiente sumador.

Centro Universitario UAEM Zumpango

### **SUMADOR BINARIO (2/2)**

Centro Universitario UAEM Zumpango

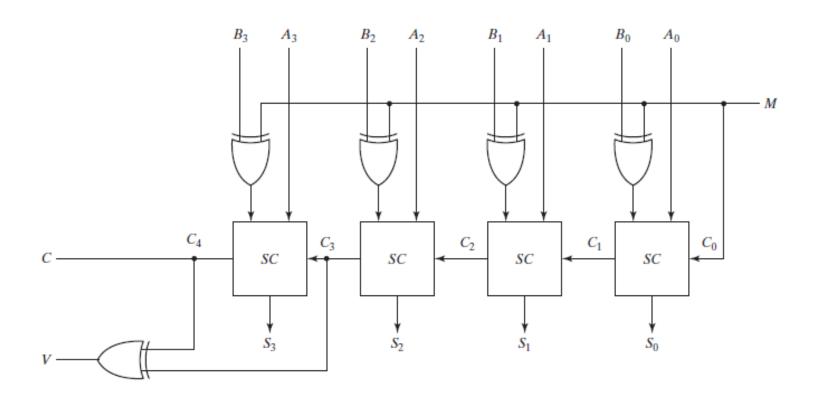

### **RESTADOR BINARIO (1/2)**

- El restador binario es un circuito combinacional que realiza la resta de dos números binarios.

- El circuito también es posible construirlo por medio de sumadores completos conectados en cascada, únicamente se complementa la entrada x.

- El acarreo de salida de cada sumador completo se conecta al acarreo de entrada del siguiente sumador.

Centro Universitario UAEM Zumpango

# **RESTADOR BINARIO (2/2)**

Centro Universitario UAEM Zumpango

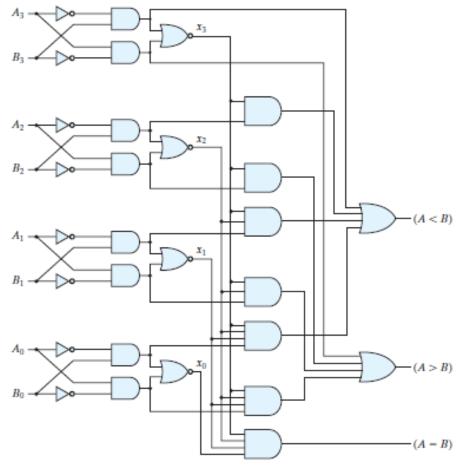

### **COMPARADOR DE MAGNITUD (1/4)**

- El comparador de magnitud es un circuito combinacional que compara dos números binarios A y B y determina sus magnitudes relativas

- El circuito cuenta con tres salidas: A > B, A < B y A = B.</li>

- El circuito para comparar dos números de *n* bits tiene 2<sup>2n</sup> combinaciones.

Centro Universitario UAEM Zumpango

### **COMPARADOR DE MAGNITUD (2/4)**

$$A = A_3 A_2 A_1 A_0$$

si  $x_i = A_i B_i + A_i B_i$ , para  $i = 0, 1, 2, 3$

$B = B_3 B_2 B_1 B_0$

Los números son iguales cuando:

$$A_3 = B_3, A_2 = B_2, A_1 = B_1 \text{ y } A_0 = B_0$$

$A = B = x_3 x_2 x_1 x_0$

A > B, cuando:

$$A > B = A_3 B_3' + x_3 A_2 B_2' + x_3 x_2 A_1 B_1' + x_3 x_2 x_1 A_0 B_0'$$

Centro Universitario UAEM Zumpango

### **COMPARADOR DE MAGNITUD (3/4)**

• **A < B,** cuando:

$$A < B = A_3 B_3 + x_3 A_2 B_2 + x_3 x_2 A_1 B_1 + x_3 x_2 x_1 A_0 B_0$$

Centro Universitario UAEM Zumpango

# **COMPARADOR DE MAGNITUD (4/4)**

Centro Universitario UAEM Zumpango

### REFERENCIAS (1/2)

- 1. Mandado, Enrique "Sistemas electrónicos digitales" 7º Edición Ed. Marcombo (1992) Barcelona ISBN 8426711707.

- Morris, M. Mano "Diseño digital" Ed. Prentice Hall (2003) México ISBN 9702604389.

- 3. Tocci, Ronald J; Widmer, Noel S. "Sistemas digitales, principios y aplicaciones" Ed. Pearson Educación de México (2003) México 8ª Edición ISBN 9702602971.

- 4. Hill, Frederick J.; Peterson, Gerald R. "Introduction to switching theory and logical design" Ed. John Wiley & sons (1981) New York 3a Edición ISBN 0471042730.

Centro Universitario UAEM Zumpango

### REFERENCIAS (2/2)

- 5. Téllez, G.R. "Notas para el curso de circuitos lógicos" Vol. 1 Impresos Instituto Politécnico Nacional (1990) México.

- 6. García Guerra, Hugo "Diseño computacional de circuitos lógicos" Instituto tecnológico de la ciudad de Madero (1995).

- 7. Motorota; Texas Instruments; Nacional Semiconductor "Manual de circuitos integrados digitales. Familia TTL".